**RoHS** Compliant

## MAP8802B CRM PFC Controller

## **General Description**

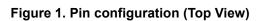

The MAP8802B is an active power factor correction (PFC) controller for boost PFC applications that operates in critical conduction mode (CRM)

In CRM operation, the on time is constant during the ac line cycle and the off time varies with the instantaneous input voltage.

The voltage mode CRM PFC controller does not need the input voltage sense line. It can reduce power loss. CRM operation is an ideal choice for medium power (100W ~ 300W) PFC boost stages with the zero current switching of DCM operation.

MAP8802B provides protection functions such as overvoltage protection, under-voltage protection, open feedback loop protection, overcurrent protection, PFC output/bypass diode short protection, and ZCD winding short protection.

MAP8802B is available in an SOP-8 Pin package. The device operates over the -40°C  $\sim$  125°C temperature.

## Applications

- AC Adapter

- Ballast, Solid State Lighting

- LCD TV, Monitor

- PDP TV

- SMPS

## Features

- Near Unity Power Factor

- No Input Voltage Sensing Requirement

- Latching PWM for Cycle-by-Cycle on time Control (Voltage Mode)

- Trans-conductance Amplifier

- High Precision Voltage Reference (±1.6% over the temperature range)

- Very low startup current consumption (≤ 35uA)

- Low typical operating current consumption

- Source 500mA / Sink 800mA Totem pole gate driver

- Under-voltage lockout with hysteresis

- Pin-to-Pin compatible with industry standards

- This is a Pb-Free and Halide-Free Device

- ZCD Short protection

## **Protection function**

- Boost diode short Protection

- Bypass diode short Protection.

- ZCD winding short Protection

- Overvoltage Protection

- Overcurrent Protection

- Under-voltage Protection

- Open/Floating feedback Protection

## **Ordering Information**

| Part Number | Top<br>Marking | Ambient<br>Temperature Range | Package                                  | Pb-Free |

|-------------|----------------|------------------------------|------------------------------------------|---------|

| MAP8802B    | MAP8802B       | -40°C ~ 125°C                | 8-Lead Small Outline Package (SOP-8 Pin) | YES     |

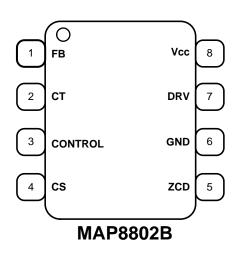

## **Pin Description**

| Pin<br>NO | Name            | Description                                                                                                                                                                                                                     |

|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | FB              | The FB pin is the inverting input of the internal error amplifier. The output voltage of the boost PFC converter should be resistively divided to 2.5V.                                                                         |

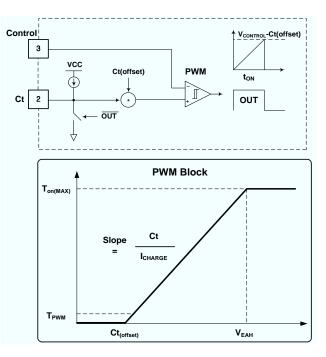

| 2         | СТ              | The CT pin sources a current to charge an external timing capacitor. The circuit controls the power switch on time by comparing the CT voltage to an internal voltage derived from V <sub>CONTROL</sub>                         |

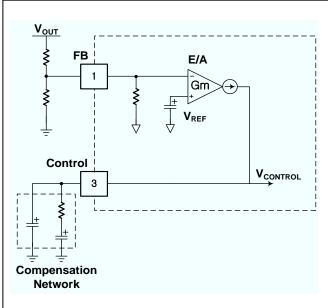

| 3         | CONTROL         | The Control pin is the output of the internal error amplifier. A compensation network is connected between the control pin and ground to set the loop bandwidth.                                                                |

| 4         | CS              | The CS pin limits the cycle-by-cycle current through the power switch. When the CS voltage exceeds $V_{\text{ILIM}}$ , the drive turns off. The sense resistor that connects to the CS pin programs the maximum switch current. |

| 5         | ZCD             | The ZCD pin is the zero current detection pin. When the voltage of this pin goes lower than 0.7V, the MOSFET is turned on.                                                                                                      |

| 6         | GND             | The GND pin is signal ground.                                                                                                                                                                                                   |

| 7         | DRV             | GATE driver output for external boost MOSFET                                                                                                                                                                                    |

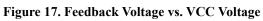

| 8         | V <sub>CC</sub> | The V <sub>CC</sub> pin is the positive supply of the controller. The controller is enabled when V <sub>CC</sub> exceeds $V_{CC(ON)}$ and is disabled when V <sub>CC</sub> decreases to less than $V_{CC(OFF)}$ .               |

### **Datasheet Version 1.1**

## **Absolute Maximum Ratings**

Stresses exceeding Maximum Ratings may damage the device. Functional operation above the recommended operating conditions is not guaranteed. Extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol              | PARAMETER                                | VALUE                   | UNIT |

|---------------------|------------------------------------------|-------------------------|------|

| V <sub>FB</sub>     | FB Voltage                               | -0.3 to 9               | V    |

| IFB                 | FB Current                               | ±10                     | mA   |

| Vст                 | Ct Voltage                               | -0.3 to 9               | V    |

| Іст                 | Ct Current                               | ±10                     | mA   |

| VCONTROL            | Control Voltage                          | -0.3 to Vcontrol(clamp) | V    |

| ICONTROL            | Control Current                          | -2 to 10                | mA   |

| Vcs                 | CS Voltage                               | -0.3 to 20              | V    |

| lcs                 | CS Current                               | ±10                     | mA   |

| Vzcd                | ZCD Voltage                              | -0.3 to Vzcd(clamp)     | V    |

| Izcd                | ZCD Current                              | ±10                     | mA   |

| Vout                | OUT Voltage                              | -0.3 to V <sub>CC</sub> | V    |

| Iout(sink)          | OUT Sink Current                         | 800                     | mA   |

| lout(source<br>)    | OUT Source Current                       | 500                     | mA   |

| V <sub>cc</sub>     | V <sub>CC</sub> Supply Voltage           | -0.3 to 20              | V    |

| lcc                 | Icc Supply Current                       | ±20                     | mA   |

| PD                  | Power Dissipation( $T_A = 70^{\circ}C$ ) | 785                     | mW   |

| Roja                | Thermal Resistance Junction-to-Ambient   | 101.9                   | °C/W |

| TJ                  | Operating Junction Temperature Range     | -40 to 125              | °C   |

| T <sub>J(MAX)</sub> | Maximum Junction Temperature             | 150                     | °C   |

| Тятд                | Storage Temperature Range                | -65 to 150              | °C   |

| TL                  | Lead Temperature (Soldering, 10s)        | 300                     | °C   |

| ESD                 | HBM on All Pins <sup>(1)</sup>           | ±5,000                  |      |

| ESD                 | MM on All Pins <sup>(1)</sup>            | ±400                    | V    |

Notes:

1. Human Body Model (HBM) per JESD22-A for all pins / Machine Model (MM) per JESD22-A 115 for all pins.

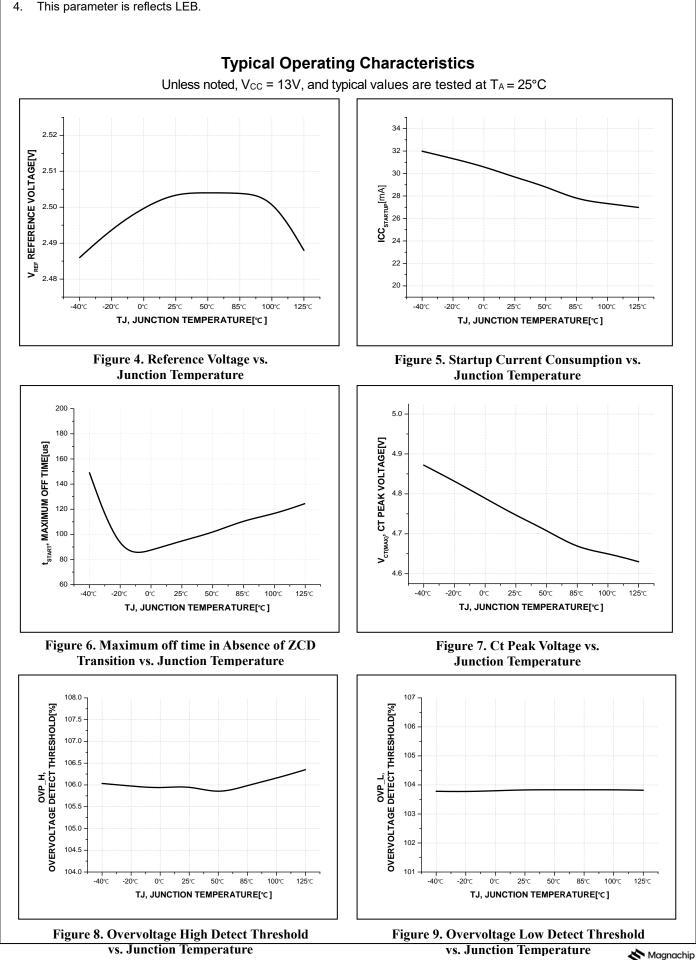

## **Electrical Characteristics**

Unless noted,  $V_{\text{CC}}$  = 13V, and typical values are tested at  $T_{\text{A}}$  = 25°C

| Symbol                                                        | Characteristic                                       | Conditions                                                                                                                       | Min      | Тур        | Max.     | Unit |

|---------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------|------------|----------|------|

| STARTUP                                                       | AND SUPPLY CIRCUITS                                  |                                                                                                                                  |          |            |          |      |

| Vcc(on)                                                       | Startup Voltage Threshold                            | V <sub>CC</sub> Increasing                                                                                                       | 11       | 12         | 13       | V    |

| VCC(OFF)                                                      | Minimum Operating Voltage                            | V <sub>CC</sub> Decreasing                                                                                                       | 8.8      | 9.5        | 10.2     | V    |

| HUVLO                                                         | Supply Voltage Hysteresis                            |                                                                                                                                  | -        | 2.5        | -        | V    |

| ICC(Startup)                                                  | Startup Current Consumption                          | 0V < V <sub>CC</sub> < V <sub>CC(ON)</sub> -200mV                                                                                | -        | 24         | 35       | μA   |

| I <sub>CC1</sub>                                              | No Load Switching<br>Current Consumption             | $C_{OUT}$ = open, 70kHz Switching,<br>V <sub>CS</sub> = 0V                                                                       | -        | 1.4        | 1.7      | mA   |

| I <sub>CC2</sub>                                              | Switching Current Consumption                        | $C_{OUT} = 1nF$ , 70kHz Switching,<br>V <sub>CS</sub> = 0V                                                                       | -        | 2.4        | 2.9      | mA   |

| I <sub>CC(fault)</sub>                                        | Fault Condition<br>Current Consumption               | No Switching, $V_{FB} = 0V$                                                                                                      | -        | 1.2        | 1.45     | mA   |

| ERROR AN                                                      | IPLIFIER SECTION                                     |                                                                                                                                  |          | •          | •        |      |

| VREF                                                          | Voltage Reference                                    | $T_A = 25^{\circ}C$                                                                                                              | 2.475    | 2.500      | 2.525    | V    |

| $\bigtriangleup V_{\text{REF1}}$                              | Voltage Reference Line Regulation                    | $V_{CC(ON)}$ + 200mV < $V_{CC}$ < 20V                                                                                            | -10      | -          | 10       | mV   |

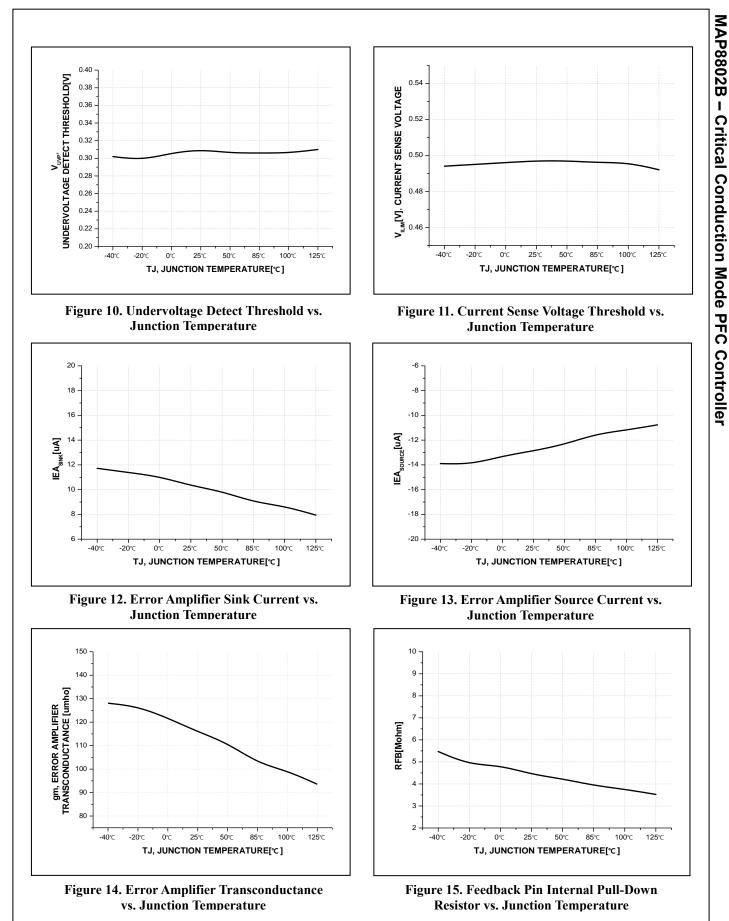

| $\bigtriangleup V_{\text{REF2}}$                              | Temperature Stability of VREF (2)                    |                                                                                                                                  | -1.6     | -          | 1.6      | %    |

| I <sub>EA</sub><br>(SINK/SOURCE)<br>I <sub>EA</sub> (SINK)OVP | Error Amplifier Current Capability                   | V <sub>FB</sub> = V <sub>REF</sub> ±0.1V<br>V <sub>FB</sub> = 1.08 * V <sub>REF</sub> or V <sub>REF</sub> + 0.2V                 | 6<br>20  | 10<br>50   | 20<br>80 | uA   |

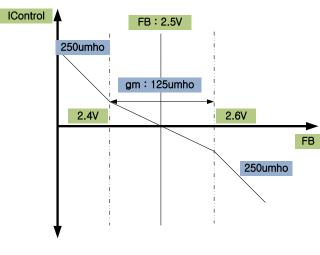

| Gm                                                            | Trans conductance                                    | V <sub>FB</sub> = V <sub>REF</sub> ±0.1V<br>V <sub>FB</sub> > V <sub>REF</sub> + 0.2V, V <sub>FB</sub> < V <sub>REF</sub> - 0.2V | 105<br>- | 125<br>250 | 145<br>- | µmho |

| Rfb                                                           | Feedback Pin Internal Pull Down<br>Resistor          | $V_{FB} = V_{UVP} \text{ to } V_{REF}$                                                                                           | 2        | 4.6        | 10       | MΩ   |

| IFB                                                           | Feedback Bias Current                                | V <sub>FB</sub> = 2.5V                                                                                                           | 0.25     | 0.54       | 1.25     | μA   |

| ICONTROL                                                      | Control Bias Current                                 | $V_{FB} = 0V$                                                                                                                    | -1       | -          | 1        | μA   |

| VEAH                                                          | Maximum Control Voltage                              | $I_{CONTROL(PULL UP)} = 10uA,$<br>$V_{FB} > V_{REF}$ ( $V_{FB} = V_{REF} + 0.1V$ )                                               | 5        | 5.5        | 6        | V    |

| Ct <sub>(offset)</sub>                                        | Minimum Control Voltage to<br>Generate output Pulses | V <sub>CONTROL</sub> = Decreasing until<br>V <sub>OUT</sub> is low, V <sub>CT</sub> = 0V                                         | 0.37     | 0.65       | 0.88     | V    |

| $V_{\text{EA}(\text{DIFF})}$                                  | Control Voltage Range                                | $V_{\text{EAH}} - Ct_{(\text{offset})}$                                                                                          | 4.5      | 4.9        | 5.3      | V    |

| CURRENT                                                       | SENSE SECTION                                        |                                                                                                                                  |          |            |          |      |

| t <sub>LEB</sub>                                              | Leading Edge Blanking Duration                       | $V_{CS} = 0V, V_{OUT} = 90\%$ to 10%                                                                                             | 100      | 190        | 350      | ns   |

| tcs                                                           | Overcurrent Detection Propagation Delay              | dV/dt = 10V/us<br>V <sub>CS</sub> = V <sub>ILIM</sub> to V <sub>OUT</sub> = 10%                                                  | 40       | 100        | 170      | ns   |

| lcs                                                           | Current Sense Bias Current                           | V <sub>CS</sub> = 2V                                                                                                             | -1       | -          | 1        | μA   |

## **Electrical Characteristics**

Unless noted,  $V_{CC}$  = 13V, and typical values are tested at  $T_A$  = 25°C

| Symbol                     | Characteristic                                                    | Conditions                                                                                                                 | Min   | Тур     | Max.     | Unit |

|----------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------|---------|----------|------|

| RAMP CON                   | ITROL SECTION                                                     | I                                                                                                                          |       |         |          |      |

| V <sub>Ct(MAX)</sub>       | Ct Peak Voltage                                                   | V <sub>Control</sub> = open                                                                                                | 4.575 | 4.93    | 5.025    | V    |

| ICharge                    | Ontime Capacitor Charge Current (2)                               | $V_{Control} = open$<br>$V_{Ct} = 0V$ to $V_{Ct(MAX)}$                                                                     | 235   | 275     | 297      | μΑ   |

| $t_{Ct(\text{Discharge})}$ | Ct Capacitor Discharge Duration (2)                               | $V_{Control} = open$<br>$V_{Ct}=V_{Ct(MAX)} - 100mV$ to 500mV                                                              | -     | 50      | 150      | ns   |

| tрwм                       | PWM Propagation Delay <sup>(2)</sup>                              | dV/dt = 30V/us<br>V <sub>Ct</sub> = V <sub>Control</sub> - Ct (offset) to V <sub>OUT</sub> = 10%                           | -     | 130     | 220      | ns   |

| MAX FREQ                   | UENCY LIMIT SECTION                                               |                                                                                                                            |       |         |          | •    |

| f <sub>MAX</sub>           | Maximum Switching Frequency                                       |                                                                                                                            | -     | 300     | 400      | kHZ  |

| ZERO CUR                   | RENT DETECTON                                                     |                                                                                                                            |       |         |          |      |

| Vzcd(ARM)                  | ZCD Arming Threshold                                              | V <sub>ZCD</sub> = Increasing                                                                                              | 1.25  | 1.4     | 1.55     | V    |

| VZCD(TRIG)                 | ZCD Triggering Threshold                                          | V <sub>ZCD</sub> = Decreasing                                                                                              | 0.6   | 0.7     | 0.83     | V    |

| V <sub>ZCD(HYS)</sub>      | ZCD Hysteresis                                                    |                                                                                                                            | -     | 700     | -        | mV   |

| Izcd                       | ZCD Bias Current                                                  | V <sub>ZCD</sub> = 5V                                                                                                      | -2    | -       | +2       | μA   |

| VCL(POS)                   | Positive Clamp Voltage                                            | I <sub>ZCD</sub> = 3mA                                                                                                     | 4.5   | 6       | 7.5      | V    |

| VCL(NEG)                   | Negative Clamp Voltage                                            | I <sub>ZCD</sub> = -2mA                                                                                                    | -0.9  | -0.7    | -0.5     | V    |

| tzco                       | ZCD Propagation Delay                                             | V <sub>ZCD</sub> = 2V to 0V ramp,<br>dV/dt = 20V/us<br>V <sub>ZCD</sub> = V <sub>ZCD(TRIG)</sub> to V <sub>OUT</sub> = 90% | -     | 100     | 170      | ns   |

| t <sub>SYNC</sub>          | Minimum ZCD Pulse Width (2)                                       |                                                                                                                            | -     | 70      | -        | ns   |

| t <sub>Start</sub>         | Maximum Off Time in Absence of ZCD Transition                     | Falling V <sub>OUT</sub> = 10% to<br>Rising V <sub>OUT</sub> = 90%                                                         | 75    | 165     | 300      | μs   |

| OUTPUT SI                  | ECTION                                                            |                                                                                                                            | 1     | 1       | I        |      |

| R он<br>R о∟               | Output Resistance (2)                                             | ISOURCE = 100mA<br>ISINK = 100mA                                                                                           | -     | 12<br>6 | 20<br>13 | Ω    |

| t <sub>rise</sub>          | Rise Time                                                         | 10% to 90%                                                                                                                 | -     | 35      | 80       | ns   |

| t <sub>fall</sub>          | Fall Time                                                         | 90% to 10%                                                                                                                 | -     | 25      | 70       | ns   |

| V <sub>DRV(start)</sub>    | Output Low Voltage                                                | $V_{CC} = V_{CC(ON)} - 200 \text{mV}, I_{SINK} = 10 \text{mA}$                                                             | -     | -       | 0.2      | V    |

| PROTECTIO                  | ON                                                                | •                                                                                                                          | I     | I       |          | •    |

| VILIM                      | Current Sense Voltage Threshold (4)                               |                                                                                                                            | 0.45  | 0.5     | 0.55     | V    |

| VOVP                       | Overvoltage Detect Threshold                                      | V <sub>FB</sub> = Increasing                                                                                               | 104   | 106     | 108      | %    |

| Vovp(hys)                  | Overvoltage Hysteresis                                            |                                                                                                                            | 20    | 50      | 90       | mV   |

| tovp                       | Overvoltage Detect Threshold<br>Propagation Delay <sup>(2)</sup>  | V <sub>FB</sub> = 2V to 3V ramp, dV/dt = 1V/us<br>V <sub>FB</sub> = V <sub>OVP</sub> to V <sub>OUT</sub> = 10%             | -     | 500     | 800      | ns   |

| VUVP                       | Undervoltage Detect Threshold                                     | V <sub>FB</sub> = Decreasing                                                                                               | 0.23  | 0.31    | 0.4      | V    |

| tuvp                       | Undervoltage Detect Threshold<br>Propagation Delay <sup>(2)</sup> | V <sub>FB</sub> = 1V to 0V ramp, dV/dt = 10V/us<br>V <sub>FB</sub> = V <sub>UVP</sub> to V <sub>OUT</sub> = 10%            | 100   | 200     | 300      | ns   |

| V <sub>DSP</sub>           | Diode short protection <sup>(3) (4)</sup>                         |                                                                                                                            |       | 2.4     |          | V    |

Notes:

2. This parameters are not production tested: Guaranteed by design correlation.

3. This parameter is influenced by board pattern. So we are recommended that connect to bid at MOSFET drain current path.

MAP8802B – Critical Conduction Mode PFC Controller

19 20

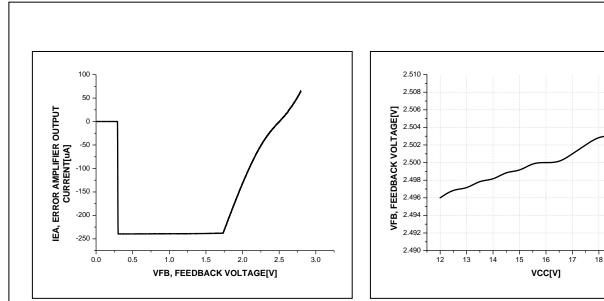

Figure 16. Error Amplifier Output Current vs. Feedback Voltage

## **Application Information**

#### 1. Start up

Generally, if the V<sub>CC</sub> voltage goes to V<sub>CC(ON)</sub>, the IC's internal blocks are enabled. The low startup current consumption (<35uA) enables minimized standby power dissipation. The V<sub>CC</sub> voltage should be higher than 9.5V under normal conditions after start-up.

Figure 18. Startup circuit

#### 2. FB Block

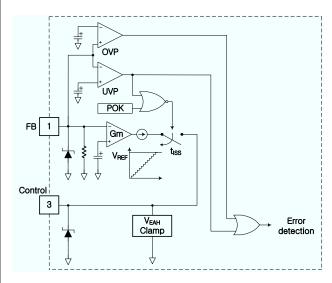

Scaled-down voltage from the output is the input for the FB pin. The used trans-conductance amplifier is good for the implementation of OVP and disables functions. The output current of the amplifier varies according to the voltage difference. The MAP8802B features comprehensive protection against open feedback loop conditions by including OVP, UVP, and FBP. Figure 19 illustrates three conditions in which the feedback loop is open.

Figure 19. Open Feedback Loop Protection

The  $\ensuremath{\textbf{UVP}}$  comparator detects an UVP fault, the drive and error amplifier are disabled.

The **OVP** comparator detects an OVP fault and the drive is disabled.

The **FB** is floating. The internal pull down resistor  $R_{FB}$  pulls down the FB voltage below  $V_{UVP}$ . The UVP comparator detects an UVP fault, the drive and error amplifier are disabled.

## 3. Ct Block

The MAP8802B controls the on time with the capacitor connected to the Ct pin. A current source charges the Ct capacitor to a voltage derived from the Control pin voltage ( $V_{Ct(off)}$ ). When  $V_{Ct(off)}$  is reached, the drive turns off.(Figure 20. Turn on Time Regulation) The Ct capacitor is sized to ensure that the required on time is reached at maximum output power and the minimum input voltage condition. The Ct pin discharges the external timing capacitor at the end of the on time.

Figure 20. Turn on Time Regulation

#### 4. Control Block

The scaled output is compared with the internal reference voltage and sinking or sourcing current is generated from the control pin by a trans-conductance amplifier. The error amplifier output is compared with the saw-tooth waveform created at the Ct. When load is heavy, output voltage decreases, scaled output decreases, Control voltage increases to compensate low output. The maximum of V<sub>CONTROL</sub> is limited to 5.5V and switching stops when Ct<sub>(offset)</sub> is lower than 0.65V. The pre-converter is compensated to ensure stability over the input voltage and output power range. To compensate the loop, a compensation network is connected between the Control and ground pins.

To ensure high PF, the bandwidth of the loop is set below 20Hz. Compensation network is selected for this design to increase the phase margin.

The compensation network is shown in Figure 21.

Figure 21. Compensation Network

For the transconductance error amplifier side, gain changes based on differential input. When the error is large, gain is large to make the output dip or peak to suppress quickly. When the error is small, low gain is used to improve power factor performance.

Figure 22. Gain Change

## 5. Error Amplifier Block

The error amplifier block consists of a OVP comparator, a transconductance amplifier and a UVP comparator. This enables the FB pin to be used for sensing overvoltage or under voltage conditions independently of the error amplifier. The MAP8802B regulates the boost output voltage using an internal error amplifier (E/A). The negative terminal of the EA is pinned out to FB, the positive terminal is connected to a  $2.5V\pm1.6\%$  reference, and the EA output is pinned out to Control. A feature of using a transconductance type amplifier is that the FB pin voltage is only determined by the resistor divider network connected to the output voltage, not the operation of the amplifier. (See Figure21)

## 6. "Overshoot-less" Startup

Feedback control speed of PFC is quite slow. Due to the slow response, there is a gap between output voltage and feedback control. That is why over-voltage protection (OVP) is critical at the PFC controller and voltage dip caused by fast load changes from light to heavy is diminished by a bulk capacitor. OVP is easily triggered at startup phase. Operation on and off by OVP at startup may cause audible noise and can increase voltage stress at startup, which is normally higher than in normal operation. This operation is better when startup time is very long. However, too long startup time enlarges the output voltage building time at light load. MAP8802B has "overshoot-less" control at startup. During startup, the feedback loop is controlled by an internal proportional gain controller and when the output voltage reaches the rated value, it switches to an external compensator after a transition time. In short, an internal proportional gain controller eliminates overshoot at startup and an external conventional compensator takes over successfully afterward.

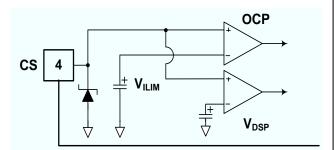

## 7. CS Block

The MOSFET current is sensed using an external sensing resistor for over-current protection. If the CS pin voltage is higher than 0.5V, the over-current protection comparator generates a protection signal. If the boost diode is shorted, the very high current flows through the MOSFET and then the MOSFET is damaged. MAP8802B has a comparator to generate a protection signal if the CS pin voltage is higher than 2.4V. At this time, DRV signal to be off and that is not start operation before VCC is up to UVLO voltage. And to more stable operation of DSP, we are recommend that connect to bid at MOSFET drain current path.

Figure 23. Diode Short Protection

#### Datasheet Version 1.1

MAP8802B – Critical Conduction Mode PFC Controller

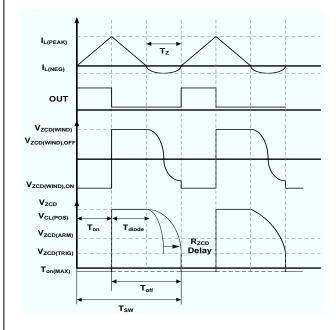

signal of the MOSFET when the boost inductor current reaches zero using auxiliary winding coupled to the boost inductor. To activate the ZCD detector of the MAP8802B, the ZCD turns ratio is sized such that at least  $V_{ZCD}$  pin during all operating conditions. (See Figure 24) The ZCD pin is protected internally by two clamps, positive clamp voltage is 6.0V and negative clamp voltage is -0.7V. When the auxiliary voltage is higher than 10V, current is sinked through a resistor from the auxiliary winding to the ZCD pin.

#### Figure 24. Realistic operation using a ZCD winding

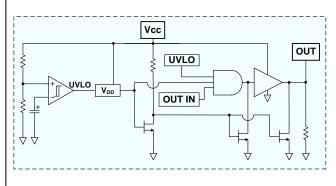

#### 9. Gate output Driver

The MAP8802B includes a powerful output driver capable of sourcing 500mA and sinking 800mA. This enables the controller to drive power MOSFETs efficiently for medium power ( $\leq$ 350W) applications. Additionally, the driver stage provides both passive and active pull down clamps.(Figure 25.) The clamps are active when V<sub>CC</sub> is off and force the driver output to a voltage less than the turn on threshold voltage of a power MOSFET.

Figure 25. Output Driver Stage and Pull Down Clamps

## 10. Under-Voltage Protection

# exceeding the ratings of the PFC stage components. The MAP8802B detects excessive $V_{OUT}$ voltage and disables the driver until $V_{OUT}$ decreases. OVP ensures that Vout is within the PFC stage component ratings.

When the input voltage is applied to the PFC stage, Vout

is forced to equate to the peak of the line voltage. The

MAP8802B detects an under-voltage fault if VOUT is

unusually low, such that  $V_{FB}$  is less than  $V_{UVP}$ . During an

if there is a disconnection in the power path to CBULK or if

The low bandwidth of the feedback network causes active

PFC stages to react to changes in output load or input

voltages slowly. Consequently, there is a risk of overshoots during transient conditions. It is critical that overvoltage

protection (OVP) prevents the output voltage from

UVP fault, the drive and error amplifier are disabled.

The UVP feature protects the application

**11. Over-Voltage Protection**

ROUT1 is disconnected.

A comparator connected to the FB pin provides the OVP protection.

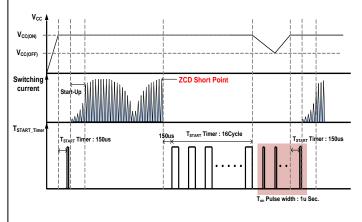

### **12. ZCD Short Protection**

#### **Max Frequency Limit**

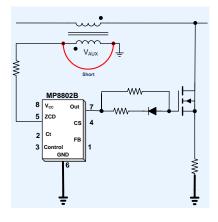

This function prevents the operation of the CCM and the burning of wires when the Aux short, (See Figure 26) The initial operation starts with CCM mode because the output voltage is lower than input. The CCM operation let the switching frequency increase until output voltage approaches the setting voltage. At this moment, the frequency is over 2MHz. MAP8802B is designed to be operated in critical conduction mode (CRM). However, when Aux short occurs, IC cannot operate with CRM mode because the ZCD voltage cannot be detected. At this moment, the operation mode is CCM and frequency is over 2MHz. Therefore, maximum frequency limit is required because the high frequency is occurred the burning of wire.

Figure 26. Aux wire short

#### Off timer protection

If ZCD noise is not existed, MAP8802B is operating as off timer (T-start timer) because ZCD signal is be absent.

But It is can be occurred audible noise because the period is about 150us.(about 6Khz) To prevent audible noise, MAP8802B detects the cycle of Tstart Timer. If Tstart Timer reached 16cycle, MAP8802B entered Auto-restart protection mode.

Figure 27. ZCD off timer protection

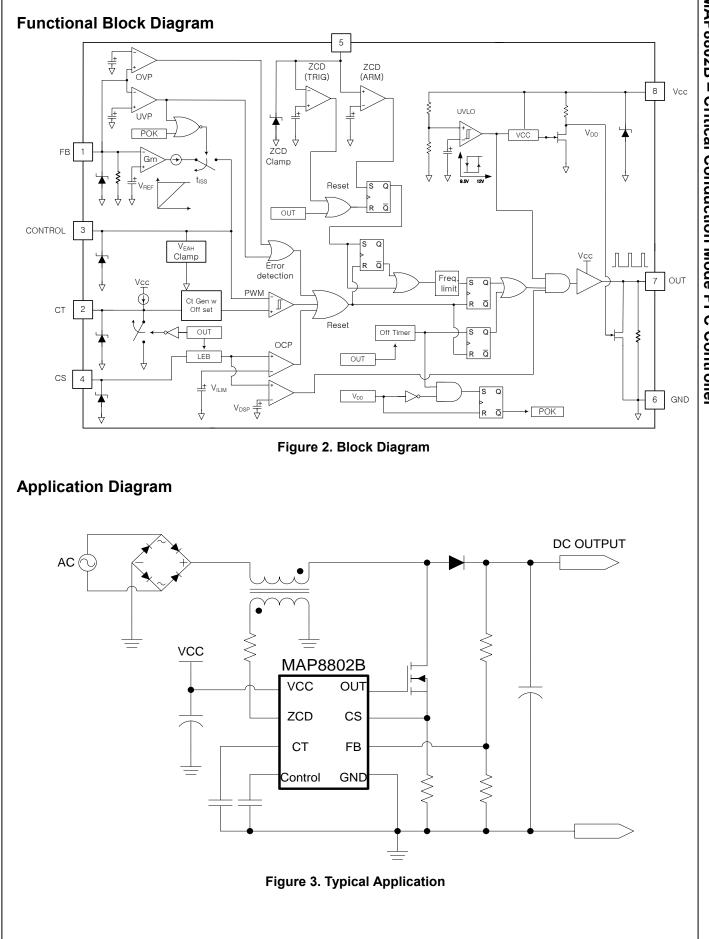

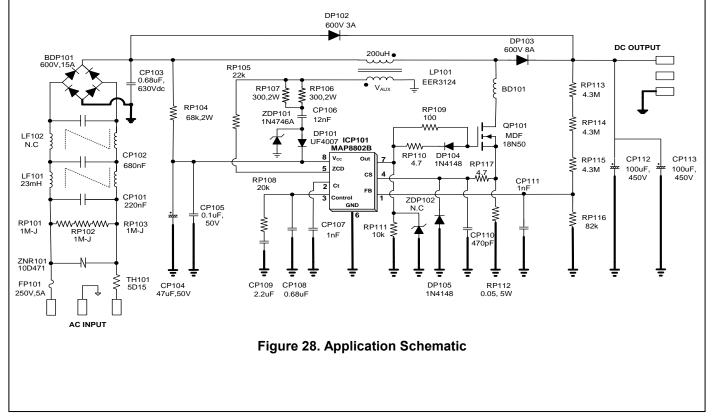

## Typical Application Circuit

## 1. Demonstration board specification.

The electronic design tool allows the user to easily determine most of the system parameters of a boost pre-converter. The demonstration board accepts a universal ac line-input voltage (85Vac~265Vac), and produces an output voltage of 400Vdc for loads up to 0.5A (PO = 200W). In demonstration board, the bypass diode (DP102) & RC resistor of CS block filter is optional. The detail demonstration design information described in our Application note.

## 2. Operating information.

| INPUT Range    | Output Power | Output Voltage |

|----------------|--------------|----------------|

| 85Vac ~ 265Vac | 200W         | 400V(0.5A)     |

## 3. Transformer information.

## 3.1 Winding specification

|      | PIN                   | WIRE    | TURNS |

|------|-----------------------|---------|-------|

| Np   | $4,5 \rightarrow 2,3$ | 0.1φ*60 | 49    |

| Insu | ation Tape            | 0.05mm  | 3     |

| Naux | $7 \rightarrow 9$     | 0.5φ*1  | 6     |

| Insu | ation Tape            | 0.05mm  | 3     |

## 3.2 Inductance & Core

|            | Pin       | Spec.      | Remark       |

|------------|-----------|------------|--------------|

| Inductance | 3,4 → 1,2 | 200μH ± 5% | 100kHz, 1V   |

| CORE       | -         | EER3124    | SAMHWA(PL-7) |

## 4. Application Schematic

## **BOM List**

## MAP8802B 200W Wide-Range Application Circuit Components List

| Part                    | Value        | Note                 | Part                       | Value                   | Note                    |

|-------------------------|--------------|----------------------|----------------------------|-------------------------|-------------------------|

| Part                    |              | Note                 | Parl                       | Value                   | Note                    |

| IC                      |              |                      | MOSFET                     |                         |                         |

| ICP101                  | MAP8802B     | MagnaChip<br>(8-SOP) | QP102                      | MDF18N50                | MagnaChip<br>(TO-220)   |

|                         | NTC          |                      | Zener Diode                |                         |                         |

| TH101                   | 5D-15        |                      | ZDP101<br>ZDP102<br>ZDP103 | 1N4746<br>N.C<br>1N4746 | Fairchild               |

|                         | Resistor     |                      | Capacitor                  |                         |                         |

| RP101                   |              |                      |                            |                         |                         |

| RP102<br>RP103          | 1M-J         | 1/8W<br>(SMD-2012)   | CP101                      | 220nF/275Vac            | X - Capacitor           |

| RP104                   | 68K-J        | 2W                   | CP102                      | 680nF/275Vac            | X - Capacitor           |

| RP105                   | 22K-J        | 1/4W<br>(SMD3216)    | CP103                      | 680nF/630Vdc            | Box capacitor           |

| RP106<br>RP107          | 300-J        | 2W                   | CP104                      | 47uF /50V               | Electrolytic Capacito   |

| RP108                   | 20K-J        | 1/8W<br>(SMD-2012)   | CP105                      | 0.1uF/50V               | Chip Capacitor          |

| RP109                   | 47-J         | 1/8W<br>(SMD-2012)   | CP106                      | 12nF/50V                | Film Capacitor          |

| RP110                   | 4.7-J        | 1/8W<br>(SMD-2012)   | CP107                      | 1nF/50V                 | Chip Capacitor          |

| RP111                   | 10K-J        | 1/8W<br>(SMD-2012)   | CP108                      | 0.68uF/16V              | Chip Capacitor          |

| RP112                   | 0.05-J       | 5W                   | CP109                      | 2.2uF/16V               | Chip Capacitor          |

| RP113<br>RP114<br>RP115 | 4.3M-F       | 1/8W<br>(SMD-2012)   | CP110                      | 470pF/50V               | Chip Capacitor          |

| RP116                   | 82K-F        | 1/8W<br>(SMD-2012)   | CP111                      | 1nF/50V                 | Chip Capacitor          |

| RP117                   | 10-J         | 1/8W<br>(SMD-2012)   | CP112                      | 420.05/4501/            | Electrolytic Consolitor |

|                         | Fuse         |                      | CP113                      | 120uF/450V              | Electrolytic Capacito   |

| FP101                   | 5.0AL/250V   |                      |                            | Diode                   |                         |

|                         | Varistor     |                      | DP101                      | UF4007(1000V 1A)        | VISHAY                  |

| ZNR101                  | 10D - 471    | 470V                 | DP102                      | UF5408(1000V 3A)        | VISHAY                  |

|                         | Line Filter  |                      | DP103                      | FSU10B60                | Nihon Inter             |

| LF101<br>LF102          | 23mH<br>N.C  | Wire0.7mm            | DP104<br>DP105             | MMBD4148                | Fairchild               |

|                         | Bridge Diode |                      |                            | Inductor                |                         |

| BDP101                  | GBJ1506      | DIODE                | LP101                      | 200uH                   | EER3124                 |

|                         | Connector    |                      |                            | -                       |                         |

| CN101<br>CN102          | YHW396-03V   |                      |                            |                         |                         |

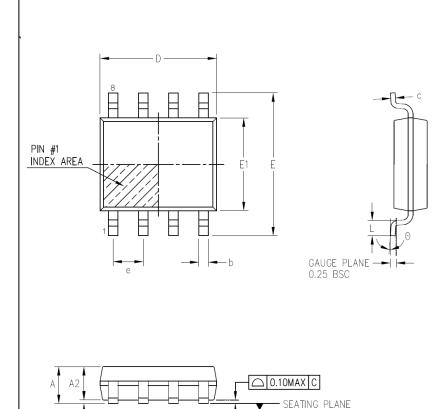

## Physical Dimensions

| Symbol | Dim      | Dimension (mm) |      |  |  |

|--------|----------|----------------|------|--|--|

| Symbol | Min Nom  |                | Max  |  |  |

| Α      | _        | _              | 1.75 |  |  |

| A1     | 0.10     | -              | 0.25 |  |  |

| A2     | 1.25     | -              | _    |  |  |

| b      | 0.31     | -              | 0.51 |  |  |

| с      | 0.10     | -              | 0.25 |  |  |

| D      | 4.90 BSC |                |      |  |  |

| E      | 6.00 BSC |                |      |  |  |

| E1     |          | 3.90 BSC       |      |  |  |

| е      | 1.27 BSC |                |      |  |  |

| L      | 0.40     | -              | 1.27 |  |  |

| Θ      | 0°       | _              | 8°   |  |  |

NOTES :

1. Reference JEDEC MS-012(AA)

2. Package length and width do not include mold flash, protrusions or gate burrs.

3. The configuration of PIN #1 identifier/chamfer feature is optional

#### DISCLAIMER:

The products are not designed for use in hostile environments, including, without limitation, aircraft, nuclear power generation, medical appliances, and devices or systems in which malfunction of any product can reasonably be expected to result in a personal injury. Seller's customers using or selling Seller's products for use in such applications do so at their own risk and agree to fully defend and indemnify Seller.

MagnaChip reserves the right to change the specifications and circuitry without notice at any time. MagnaChip does not consider responsibility for use of any circuitry other than circuitry entirely included in a MagnaChip product. Magnachip is a registered trademark of Magnachip Semiconductor Ltd.