# MAP3525B

# 2-CH Quasi-Resonant Mode Buck Controller for LED Backlight

#### **General Description**

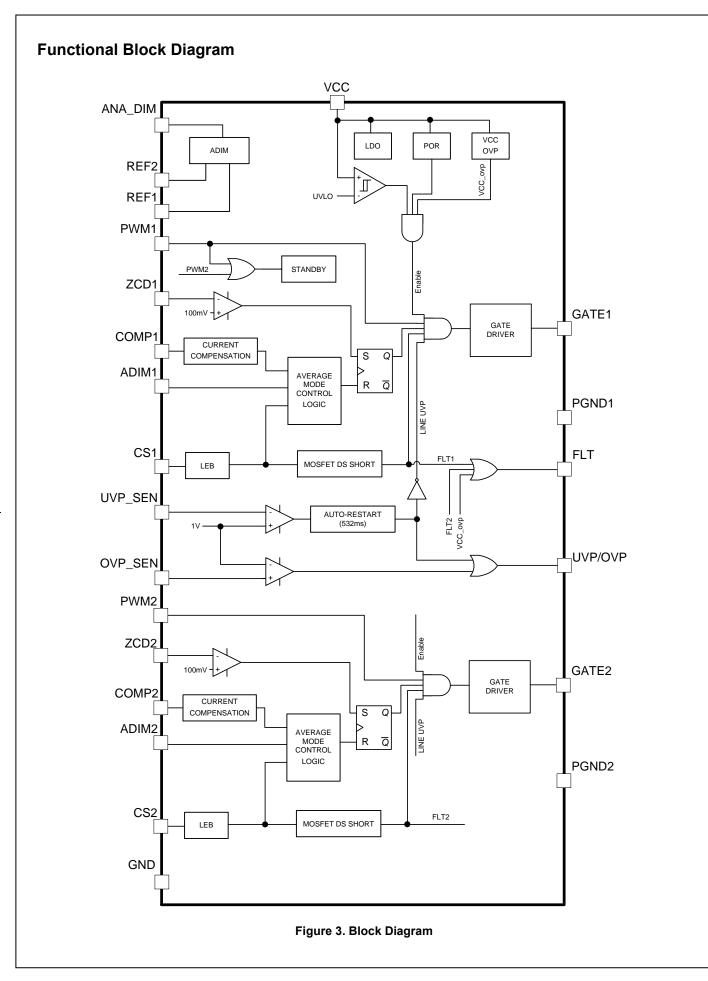

MAP3525B is a 2 channel quasi-resonant mode buck controller for LED backlight application. It operates at boundary conduction mode which provides better efficiency and lower EMI.

MAP3525B features  $\pm 2\%$  current sensing (CS) voltage accuracy and has dedicated analog dimming input up to 3.3V. It can be powered from 8.5V ~ 18V supply.

MAP3525B provides MOSFET drain-source short detection for fault output,  $V_{CC}$  over voltage protection (OVP) for fault output,  $V_{CC}$  under voltage lockout (UVLO), Input voltage OVP detection, Input voltage UVP detection, current sense resistor short protection, short circuit protection (SCP) and standby mode.

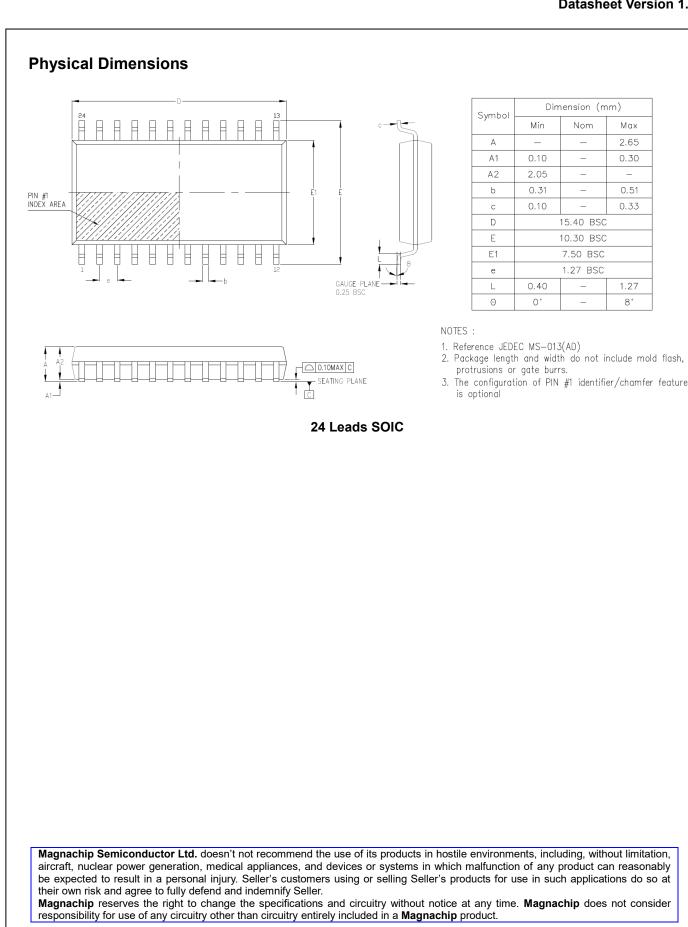

MAP3525B is available 24 leads SOP with Halogenfree (fully RoHS compliant).

RoHS Compliant

## Features

- 8.5V to 18V Input Voltage Range

- Quasi-Resonant Mode

- LED Current Compensation Function

- Direct PWM Dimming Input

- ±2% Current Sensing Voltage Accuracy

- Fault Output (FLT pin)

- MOSFET Drain-Source Short Detection

- V<sub>CC</sub> Over Voltage Protection Detection

- Short Circuit Protection

- Current Sense Resistor Short Protection

- Vcc Under Voltage Lock Out

- Input Voltage Under Voltage Protection Detection

- Input Voltage Over Voltage Protection Detection

- Standby Mode

- 24 Leads SOIC Package with Halogen-free

#### Applications

- High Brightness white LED backlighting for LCD TVs

- General LED lighting applications

#### Ordering Information

| Part Number  | Top<br>Marking | Ambient<br>Temperature Range | Package      | RoHS Status  |

|--------------|----------------|------------------------------|--------------|--------------|

| MAP3525BSIRH | MAP3525B       | -40 ℃ to +85 ℃               | 24Leads SOIC | Halogen Free |

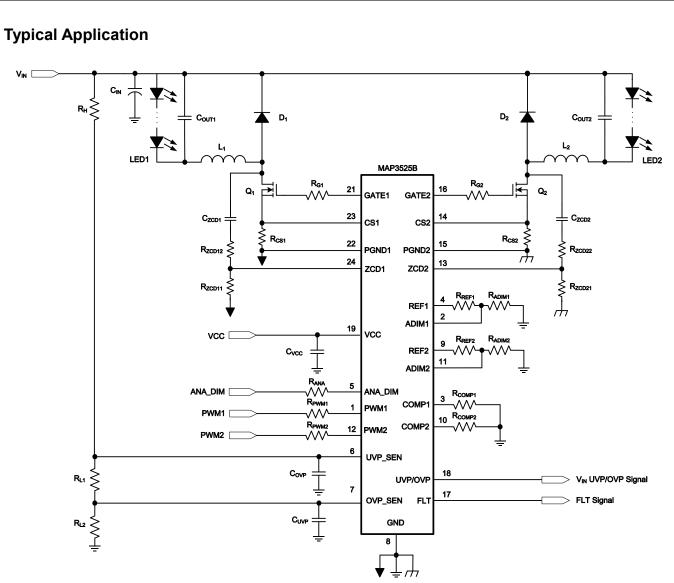

Figure 1. 2-Ch Quasi-resonant mode buck converter

# Pin Configuration and Description

Figure 2. Pin Configuration (Top View)

|     | I       |                                           |

|-----|---------|-------------------------------------------|

| Pin | Name    | Description                               |

| 1   | PWM1    | PWM Dimming for Ch1                       |

| 2   | ADIM1   | Internal Analog Dimming for Ch1           |

| 3   | COMP1   | LED Current Accuracy Compensation for Ch1 |

| 4   | REF1    | ADIM Buffer Output for Ch1                |

| 5   | ANA_DIM | External Analog Dimming Input             |

| 6   | UVP_SEN | Input Voltage UVP Detection (Note 1)      |

| 7   | OVP_SEN | Input Voltage OVP Detection (Note 1)      |

| 8   | GND     | Ground                                    |

| 9   | REF2    | ADIM Buffer Output for Ch2                |

| 10  | COMP2   | LED Current Accuracy Compensation for Ch2 |

| 11  | ADIM2   | Internal Analog Dimming for Ch2           |

| 12  | PWM2    | PWM Dimming for Ch2                       |

| 13  | ZCD2    | Zero Current Detection for Ch2            |

| 14  | CS2     | Current Sense for Ch2                     |

| 15  | PGND2   | Power Ground for Ch2 (Note 2)             |

| 16  | GATE2   | GATE Drive Output for Ch2                 |

| 17  | FLT     | Fault Output                              |

| 18  | UVP/OVP | Input Voltage UVP/OVP Signal Output       |

| 19  | VCC     | Power Supply Input                        |

| 20  | NC      | No Connection                             |

| 21  | GATE1   | GATE Drive Output for Ch1                 |

| 22  | PGND1   | Power Ground for Ch1 (Note 2)             |

| 23  | CS1     | Current Sense for Ch1                     |

| 24  | ZCD1    | Zero Current Detection for Ch1            |

**Note 1**: Connect external resistor to UVP\_SEN pin and OVP SEN pin to detect the input voltage V<sub>IN</sub> as shown in typical application **Note 2**: Connect external resistor to PGND to sense the external power MOSFET source current as shown in typical application

**Datasheet Version 1.0**

🔊 Magnachip

Sep 2022

# Absolute Maximum Ratings (Note 1)

| Symbol                                                                                                                                                                     | Parameter                                                                   | Min   | Max   | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|-------|------|

| $V_{CC}$ , $V_{GATEx}$ , $V_{PWMx}$ , $V_{FLT}$                                                                                                                            | VCC, GATEx, PWMx, FLT pins Voltage                                          | -0.3  | 20    | V    |

| V <sub>ZCDx</sub>                                                                                                                                                          | ZCDx pin Voltage                                                            | -0.7  | 20    | V    |

| V <sub>CSx</sub> , V <sub>REFx</sub> , V <sub>ADIMx</sub> , V <sub>ANA_DIM,</sub><br>V <sub>COMPx</sub> , V <sub>UVP</sub> sen, V <sub>OVP</sub> sen, V <sub>UVP/OVP</sub> | CSx, REFx, ADIMx, ANA_DIM, COMPx, UVP_SEN,<br>OVP_SEN, UVP/OVP pins Voltage | -0.3  | 5     | V    |

| T <sub>PAD</sub> Soldering Lead/ Pad Temperature 10sec                                                                                                                     |                                                                             |       | 300   | °C   |

| TJ                                                                                                                                                                         | Junction Temperature                                                        | -40   | +150  | °C   |

| Ts                                                                                                                                                                         | Storage Temperature                                                         | -65   | +150  | °C   |

|                                                                                                                                                                            | HBM on All Pins (Note 2)                                                    | -2000 | +2000 |      |

| ESD                                                                                                                                                                        | MM on All Pins (Note 3)                                                     | -200  | +200  | V    |

|                                                                                                                                                                            | CDM on All Pins (Note 4)                                                    | -500  | +500  |      |

Note 1: Stresses beyond the above listed maximum ratings may damage the device permanently. Operating above the recommended conditions for extended time may stress the device and affect device reliability. Also the device may not operate normally above the recommended operating conditions. These are stress ratings only.

Note 2: ESD tested per JESD22A-114.

Note 3: ESD tested per JESD22A-115.

Note 4: ESD tested per JESD22C-101.

# Recommended Operating Conditions (Note 1)

| Parameter            |                              | Min | Max                   | Unit |

|----------------------|------------------------------|-----|-----------------------|------|

| V <sub>cc</sub>      | Supply Input Voltage         | 8.5 | 15 <sup>(note2)</sup> | V    |

| V <sub>ANA_DIM</sub> | ANA_DIM Input Range          | 0.0 | 3.3                   | V    |

| T <sub>A</sub>       | Ambient Temperature (Note 3) | -40 | +85                   | °C   |

Note 1: Normal operation of the device is not guaranteed if operating the device over outside range of recommended conditions.

Note 2: If the supply input voltage (V<sub>CC</sub>) exceeds typ.16V, the gate signal is shut down by the V<sub>CC</sub> OVP function.

Note 3: The ambient temperature may have to be derated if used in high power dissipation and poor thermal resistance conditions.

## Package Thermal Resistance (Note 1)

|              | Parameter     | R <sub>0JA</sub> | R <sub>ejc</sub> | Unit |

|--------------|---------------|------------------|------------------|------|

| MAP3525BSIRH | 24 Leads SOIC | 39.4             | 16.9             | °C/W |

|              |               |                  |                  | -    |

Note 1: Multi-layer PCB based on JEDEC standard (JESD51-7)

|                          | V <sub>CC</sub> = 12V, C <sub>VCC</sub> = 1.0µF, and typical value<br>Parameter |                                                                  | Min  | Тур        | Max  | Unit |

|--------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------|------|------------|------|------|

| Supply                   |                                                                                 |                                                                  |      | <b>3</b> 1 |      |      |

| V <sub>cc</sub>          | Input Voltage Range                                                             |                                                                  | 8.5  |            | 18   | V    |

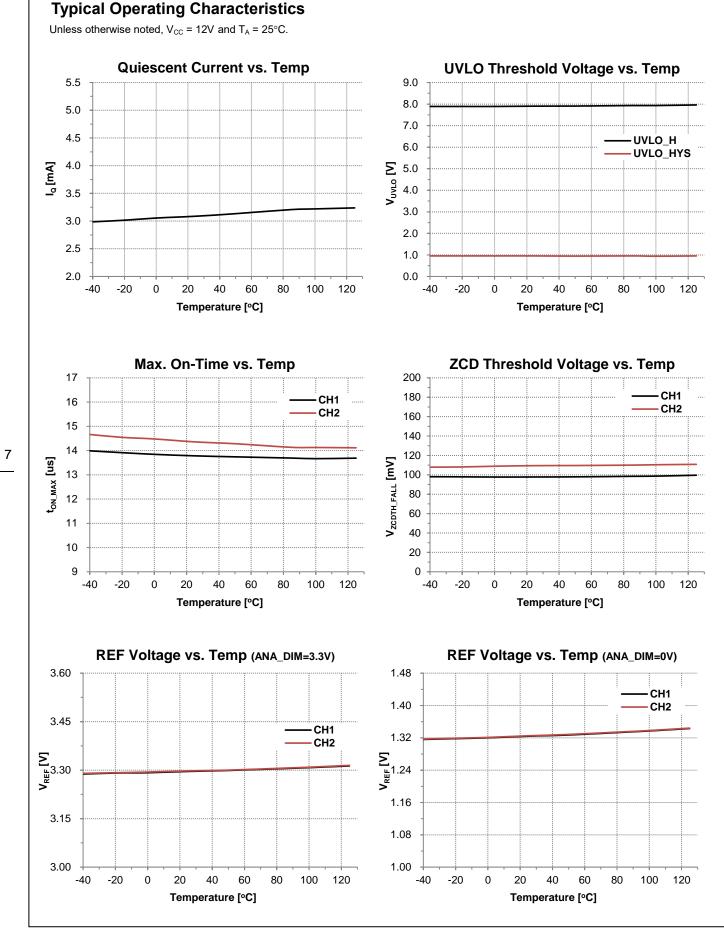

| lo                       | Quiescent Current                                                               | $V_{PWM} = 0V, V_{CC} = 12V$                                     |      | 4.0        |      | mA   |

| ISTANDBY                 | Standby Current                                                                 | $V_{CC} = 12V$                                                   |      |            | 700  | uA   |

|                          | Under Voltage Lockout                                                           | Release threshold(rising V <sub>cc</sub> )                       | 7.5  | 8.0        | 8.5  |      |

| V <sub>CC_UVLO</sub>     | Threshold Voltage on VCC pin                                                    | Lockout hysteresis(falling V <sub>CC</sub> )                     | 0.5  | 1.0        | 1.5  | V    |

| t <sub>PG_DELAY</sub>    | Power Good Delay Time                                                           |                                                                  |      | 500        |      | ms   |

| Zero-Current             | Sense                                                                           |                                                                  |      |            |      |      |

| V <sub>ZCDTH_FALL</sub>  | ZCD Threshold Voltage                                                           |                                                                  |      | 100        |      | mV   |

| V <sub>ZCDTH_RISE</sub>  | <u> </u>                                                                        | Rising V <sub>ZCD</sub>                                          |      | 200        |      | mV   |

| V <sub>ZCDHYS</sub>      | ZCD Hysteresis<br>ZCD Time-Out                                                  |                                                                  |      | 100<br>25  |      | mV   |

| t <sub>zcdtout</sub>     | ZCD Time-Out                                                                    |                                                                  |      | 25         |      | us   |

|                          | GATE Source Current                                                             | V <sub>GATE</sub> = 0V                                           |      | 300        |      | mA   |

| I <sub>SOURCE</sub>      | GATE Source Current                                                             | $V_{GATE} = 00$<br>$V_{GATE} = V_{CC} = 12V$                     |      | 600        |      | mA   |

| t <sub>RISE</sub>        | GATE Output Rising Time                                                         | $V_{GATE} = V_{CC} = 12V$<br>$C_{GATE} = 1nF, V_{CC} = 12V$      |      | 70         | 150  | ns   |

|                          | GATE Output Falling Time                                                        | $C_{GATE} = 1nF, V_{CC} = 12V$<br>$C_{GATE} = 1nF, V_{CC} = 12V$ |      | 35         | 100  | ns   |

|                          | Max. On-Time                                                                    | -Unit, +UU 12+                                                   |      | 13         | 100  | us   |

| f <sub>MAX</sub>         | Max. Frequency                                                                  |                                                                  |      | 1000       |      | kHz  |

|                          | e & Dimming                                                                     |                                                                  |      |            |      |      |

| V <sub>ADIM</sub>        | ADIM Input Voltage Range                                                        |                                                                  | 0.66 |            | 1.65 | V    |

| M                        | CS Detection Voltage                                                            | V <sub>ADIM</sub> = 0.66V                                        |      | 0.33       |      | V    |

| V <sub>CS</sub>          | CS Detection Voltage                                                            | V <sub>ADIM</sub> = 1.65V                                        |      | 0.825      |      | V    |

| <b>t</b> leb             | Leading Edge Blanking Time                                                      | (Note1)                                                          |      | 350        |      | ns   |

| REF                      |                                                                                 |                                                                  |      | 1          |      | -    |

| $V_{\text{ANA}}$ DIM     | ANA_DIM Input Voltage Range                                                     |                                                                  | 0    |            | 3.3  | V    |

|                          |                                                                                 | ANA_DIM = 0V                                                     |      | 1.32       |      | V    |

| V <sub>REF</sub>         | REF Voltage                                                                     | ANA_DIM = 3.3V                                                   |      | 3.3        |      | V    |

|                          |                                                                                 | ANA_DIM > 3.6V                                                   |      | 3.3        |      | V    |

| COMP                     |                                                                                 | ANA_DIM = open                                                   |      | 3.3        |      | V    |

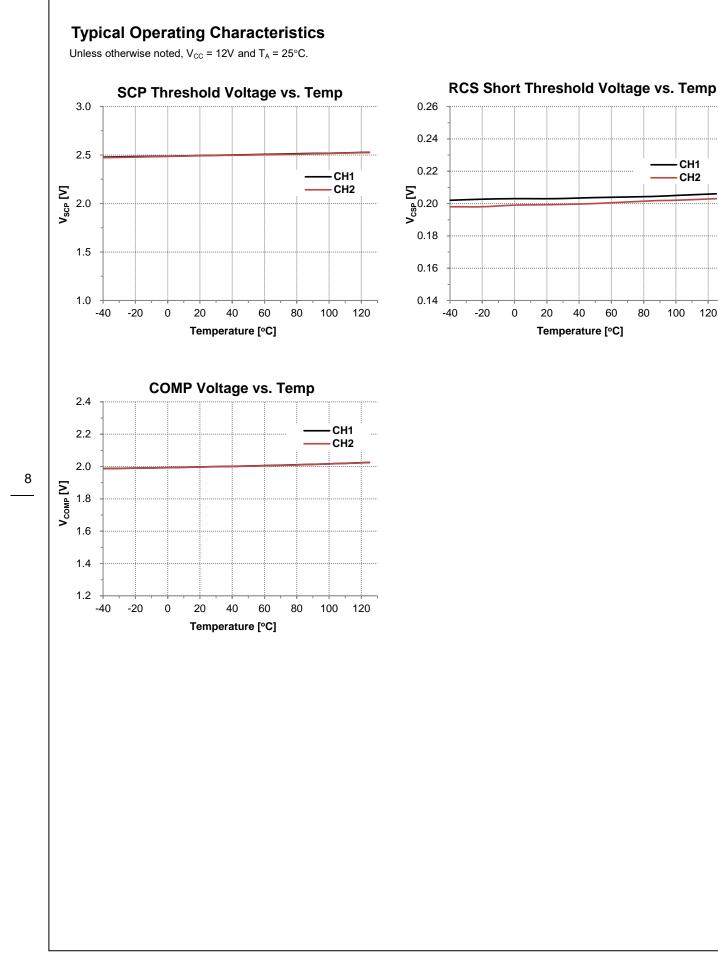

|                          | COMP Voltage                                                                    |                                                                  |      | 2          |      | V    |

| ogic Interfac            |                                                                                 |                                                                  |      | 2          |      | v    |

| -                        | Logic Input Level on                                                            | V <sub>PWM_L</sub> : Logic Low                                   |      |            | 0.8  |      |

| V <sub>PWM</sub>         | PWM pin                                                                         | V <sub>PWM H</sub> : Logic High                                  | 2.2  |            | 010  | V    |

| R <sub>PWM</sub>         | Pull-down Resistor on PWM pin                                                   | $V_{\text{PWM}} = 4V$                                            | 50   | 100        | 150  | kΩ   |

| Protection               | · ·                                                                             |                                                                  |      |            |      |      |

| V <sub>SCP</sub>         | SCP Detection Threshold Voltage<br>on CS pins                                   |                                                                  | 2.3  | 2.5        | 2.7  | V    |

| t <sub>DELAY</sub>       | SCP Delay Time                                                                  |                                                                  |      | 300        |      | ns   |

| <b>t</b> restart         | Restart Time                                                                    |                                                                  |      | 1          |      | ms   |

| V <sub>CSP</sub>         | RCS Short Detection                                                             |                                                                  | 0.15 | 0.2        | 0.25 | V    |

| t <sub>CSP</sub>         | Threshold Voltage on CS pin<br>RCS Short Detection Time                         |                                                                  |      | 5          |      | us   |

| N/                       | MOSFET DS Short Detection                                                       | V <sub>PWM</sub> = 3.3V                                          | 2.3  | 2.5        | 2.7  | V    |

| V <sub>SCPDS</sub>       | Threshold Voltage on CS pin                                                     | V <sub>PWM</sub> = 0V                                            | 0.5  | 0.7        | 0.9  | V    |

| t <sub>SCPDS</sub>       | MOSFET DS Short Detection Time                                                  |                                                                  |      | 5          |      | us   |

| R <sub>FLT</sub>         | FLT pin Internal Resistance                                                     | I <sub>FLT</sub> = 1mA                                           | 250  | 500        | 1000 | Ω    |

| $V_{CC\_OVP}$            | V <sub>cc</sub> OVP Detection threshold voltage                                 |                                                                  |      | 16         |      | V    |

| V <sub>CC_OVP_HYS</sub>  | V <sub>CC</sub> OVP Hysteresis                                                  |                                                                  |      | 1          |      | V    |

| $V_{\text{IN\_UVP/OVP}}$ | V <sub>IN</sub> UVP/OVP Detection threshold<br>voltage                          |                                                                  | 0.9  | 1          | 1.1  | V    |

| $V_{IN}_{UVP}$           | V <sub>IN</sub> UVP Detection Time                                              |                                                                  |      | 1.5        |      | us   |

| VIN_UOVP_HYS             | V <sub>IN</sub> UVP/OVP Hysteresis                                              |                                                                  |      | 100        |      | mV   |

Sep 2022

MAP3525B datasheet – Quasi-Resonant Mode Buck Controller for LED Backlight

Sep 2022

# **Functional Description**

## **GENERAL DESCRIPTION**

The MAP3525B is a low-side single switch buck controller optimized to LED backlight applications. It does not require any external loop compensation or high side current sensing.

The IC operates at boundary conduction mode which provides better efficiency and lower EMI.

## LED CURRENT

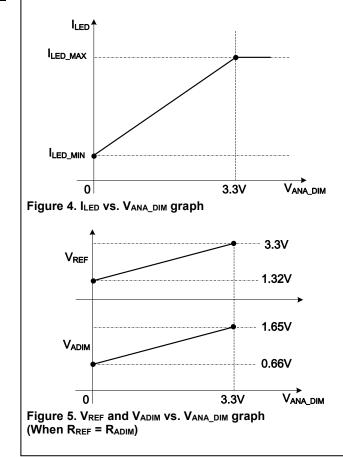

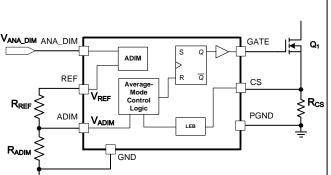

The LED current is calculated by following equation.

$$I_{LED} = \frac{0.5 V_{ADIM}}{R_{CS}}$$

$$= \frac{0.5 \times (0.66 + 0.3 \times V_{ANA\_DIM})}{R_{CS}} [A] \quad (1)$$

When  $R_{REF} = R_{ADIM}$ .

9

The ANA\_DIM voltage range is from 0.0V to 3.3V. The LED current changes according to ANA\_DIM and ADIM.

In terms of total system accuracy of LED current, the larger inductance, the slower switching frequency and the larger minimum on time than 800ns, the better accuracy.

Figure 6. Configuration of analog dimming and current sensing

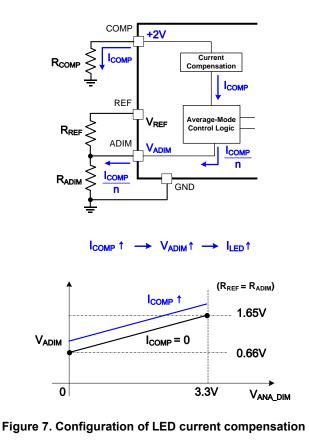

## LED CURRENT COMPENSATION

MAP3525B has the LED current compensation function by using COMP pin.

LED current offset can be occurred by the input/output condition and the components of the buck converter.

The compensation resistor  $R_{COMP}$  is used to control the offset voltage of ADIM. The COMP voltage is typ. 2V and the compensation current  $I_{COMP}$  is fixed by  $R_{COMP}.$

By Internal current compensation circuit, 1/n times  $I_{COMP}$  current flows to ADIM pin. By this current, the offset voltage of ADIM is generated. Consequently, LED current is compensated by  $R_{COMP}$ .

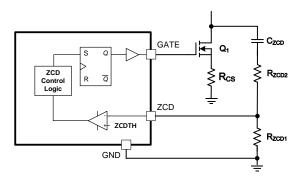

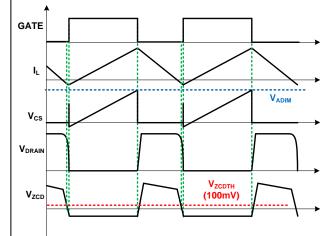

# ZERO-CURRENT SENSE

The MAP3525B is a boundary conduction mode (BCM) buck controller operating at resonant zerocurrent transition mode.

The zero detection circuit uses displacement current of a sense capacitor  $C_{ZCD}$  as shown in typical application. At the inductor current ramps down to zero, the drain voltage of MOSFET begins oscillation. As soon as the ZCD pin voltage falls down to 100mV (V<sub>ZCDTH</sub>), the MAP3525B initiates next switch cycle.

Figure 8. Configuration of analog dimming and current sensing

Figure 9. Zero-Current Sense

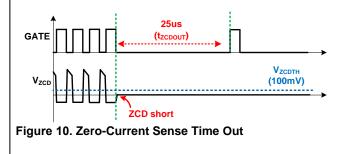

After MOSFET turned-off, if the ZCD pin voltage keeps less than typ. 100mV (V<sub>ZCDTH</sub>) for more than typ. 25us (t<sub>ZCDTOUT</sub>), the IC begins next switch cycle forcibly To prevent abnormal MOSFET turn-on by ZCD, ZCD voltage is masked for 440ns after a MOSFET is turned off internally.

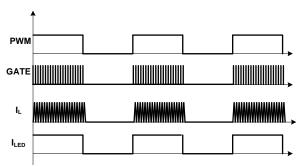

# **PWM DIMMING**

The brightness control of the LEDs is performed by a pulse-width modulation. The GATE output is valid only at PWM on period. This means that the GATE maintains off-state as long as PWM signal is logic low. Care should be taken to test at low PWM duty-cycle because the output capacitor can affect rising and falling time of LED current due to its charging and discharging time.

Figure 11. PWM Dimming

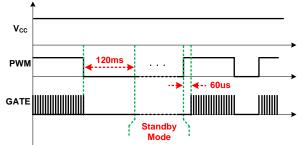

## STANDBY MODE

The MAP3525B has a standby mode to reduce the power consumption. If the PWM signal keeps a low level for more than typ. 120ms, the MAP3525B turnsoff the GATE output and goes on the standby mode. During the standby mode, if the PWM signal is high, the IC wakes up and turns-on the GATE output after typ. 60us.

Figure 12. Standby Mode

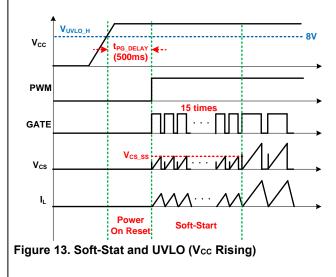

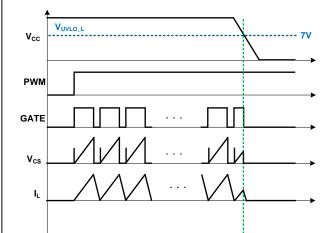

# V<sub>cc</sub> UNDER VOLTAGE LOCKOUT (UVLO)

The MAP3525B has an Internal LDO regulator to supply internal circuit and GATE driver. This LDO is powered up when the  $V_{CC}$  voltage rises to UVLO release threshold.

If the voltage on the  $V_{CC}$  pin falls below UVLO lockout threshold, the device turns-off the GATE output and be reset. This ensures fail-safe operation for  $V_{CC}$  input voltage falling.

# SOFT-START

The MAP3525B operates at peak current mode at initial start-up to smooth inductor current ramp-up

(output capacitor charging phase). The number of peak-controlled switch cycles is 15 times at initial start-up.

## **FLT OUTPUT**

FLT pin is an open-drain type output pin. If any of following events occurs, the FLT pin goes to logic Low state immediately. The protection status is latched and can be cleared by applying a complete power-on-reset (POR).

- MOSFET Drain-Source Short Detection

- V<sub>CC</sub> Over Voltage Protection (OVP)

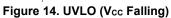

## **MOSFET DRAIN-SOURCE SHORT DETECTION**

Regardless of PWM logic state, if the CS voltage exceeds  $V_{\text{SCPDS}}$  for more than typ. 5us ( $t_{\text{SCPDS}}$ ) due to drain-source short of external MOSFET, the FLT pin goes to logic Low state immediately and the GATE output is turned off.

CASE (1) - At PWM Logic High : If the CS voltage exceeds typ. 2.5V (V<sub>SCPDS</sub>) for more than 5us, the MOSFET drain-source short protection is occurred.

#### CASE (2) - At PWM Logic Low :

If the CS voltage exceeds typ. 0.7V ( $V_{SCPDS}$ ) for more than 5us, the MOSFET drain-source short protection is occurred.

Figure 15. MOSFET Drina-Source Short Detection

## Vcc OVER VOLTAGE PROTECTION (OVP)

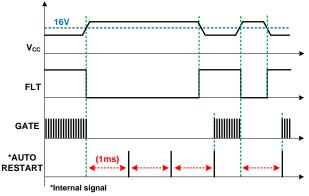

If the V<sub>CC</sub> voltage exceeds typ. 16V (V<sub>OVP</sub>), the FLT pin goes to the logic Low state immediately and the GATE output is turned off. Under the V<sub>CC</sub> OVP condition, the internal auto-restart signal occurs with 1ms period. When the V<sub>CC</sub> is less than 16V, the GATE output is turned on by the auto-restart signal. The V<sub>CC</sub> OVP function does not latch.

Figure 16. Vcc Over Voltage Protection

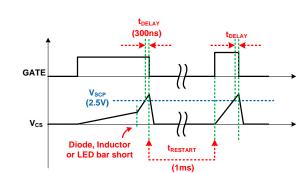

# SHORT CIRCUIT PROTECTION (SCP)

If the CS voltage rises 2.5V (V<sub>SCP</sub>) during normal operation, the MAP3525B turns-off the GATE output after typ. 300ns ( $t_{DELAY}$ ). The auto-restart time is typ. 1ms ( $t_{RESTART}$ ). This protects for hard instantaneous short such as free-wheeling diode, inductor or LED bar short.

Figure 17. Short Circuit Protection

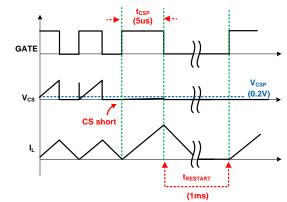

# **R**<sub>cs</sub> SHORT PROTECTION

If the CS pin is shorted to GND due to current sense resistor (R<sub>CS</sub>) short, there is a potential danger of the over-current condition not being detected. The MAP3525B can protect this short event.

If the CS pin voltage is equal or lower than typ. 0.2V (V<sub>CSP</sub>) for more than typ. 5us (t<sub>CSP</sub>), the IC turns off the GATE output immediately.

Figure 18. R<sub>cs</sub> Short Protection

12

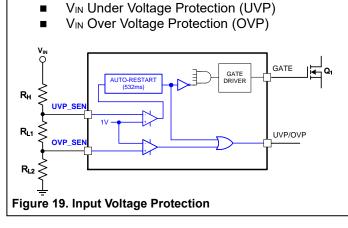

# INPUT VOLTAGE PROTECTION

MAP3525B has the UVP\_SEN pin and the OVP\_SEN pin to detect the input voltage of the QR buck converter. By using the voltage divider to connect these pins, the input voltage is detected and the under/over voltage level of the input voltage can be decided.

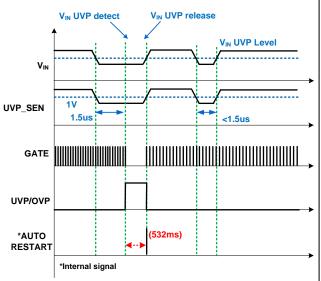

# VIN UNDER VOLTAGE PROTECTION (UVP)

If the UVP\_SEN voltage is less than typ. 1V for more than typ. 1.5us ( $V_{IN}$ \_tuvP). the GATE output is turned off, and the high signal (typ. 5V) outputs from the UVP/OVP pin, immediately. Under the  $V_{IN}$  OVP condition, the internal auto-restart signal occurs with 532ms period. When the UVP\_SEN voltage is more than typ. 1V, 1.5us ( $V_{IN}$ \_tuvP) and the internal auto-restart signal is high, the UVP/OVP output is high and the GATE output is turned off, immediately.

The input voltage UVP level,  $V_{IN\_UVP}$  is decided as follows:

$$V_{IN\_UVP} = 1 \times \frac{R_H + R_{L1} + R_{L2}}{R_{L1} + R_{L2}} \quad [V]$$

(2)

## Figure 20. V<sub>IN</sub> Under Voltage Protection (UVP)

I

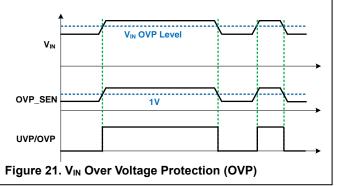

# V<sub>IN</sub> OVER VOLTAGE PROTECTION (OVP)

If the OVP\_SEN voltage is exceeds than typ. 1V, the high signal (typ. 5V) outputs from the UVP/OVP pin. When the OVP\_SEN voltage is less than typ. 1V, the UVP/OVP output is Low.

The input voltage OVP level,  $V_{\text{IN}\_\text{OVP}}$  is decided as follows:

$$V_{IN_{OVP}} = \frac{R_{L1} + R_{L2}}{R_{L2}} \times V_{IN_{UVP}}$$

[V] (3)

# **Application Information**

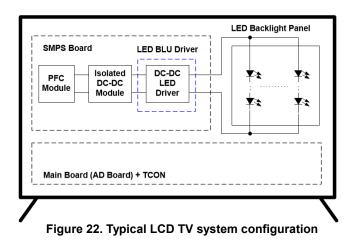

## **LED Backlight Application**

In display devices such as TV, monitor, the LED backlight unit is commonly needed for the light source. Figure 22 shows the typical LCD TV system configuration. In the SMPS board, the power factor correction (PFC) module provides high power factor and converts the AC input voltage to the DC link voltage and the isolated DC-DC module provides the regulated DC voltage with galvanic isolation.

In LED backlight panel, as the current through the LED bars increases, the brightness also increases. Therefore, the constant current should be supplied to achieve high-quality light. However, the isolated DC-DC module cannot provide constant current. Hence, the DC-DC LED driver is required to control the constant LED current.

13

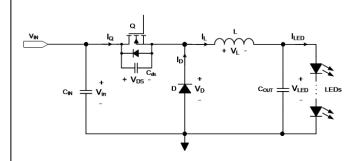

## **Buck Converter Topology**

The buck converter is known as the step-down DC-DC converter, which converts the input voltage to be lower. Figure 23 shows the circuit diagram of the conventional buck converter. In the conventional buck converter, there is a high-side switch (a floating switch) so the floating gate driver is required.

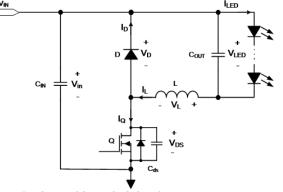

In order to simplify the control without the floating gate driver, the low-side switch buck converter has been proposed as shown in Figure 24. It is also called a floating buck converter because the output load is floating from the ground. Since the LED load do not require to connect to the ground, this topology can be adopted for LED drivers.

# **Quasi-Resonant Mode**

CIN

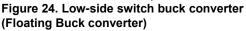

In order to operate the critical conduction mode (CRM) mode, the guasi-resonant (QR) mode is adopted as the control method. It is known as variable frequency control or valley switching control. Figure 25 shows the principle of the quasi-resonant mode at the low-side switch buck converter. In the discontinuous conduction mode (DCM) operation mode, when the stored energy of the inductor is fully discharged and the inductor current is zero, the resonance between the buck inductor L and the drain-source capacitance Cds of the MOSFET Q occurs. The MOSFET drain-source voltage V<sub>DS</sub> oscillates as a damped sinusoidal wave. The resonant frequency by the L and Cds is expressed as follows:

$$f_R = \frac{1}{2\pi\sqrt{L \cdot C_{ds}}} \tag{4}$$

Resonan

and I

(QR) switchi

In DCM operation mode

LED

-V<sub>LEC</sub>

LED

In the QR mode, the above-mentioned resonance is used as shown in Figure 25. If the MOSFET is turned on when V<sub>DS</sub> reaches zero (or low) (which is called valley point), the buck converter is operated in the CRM mode. Because the voltage and current of the MOSFET are zero (or low) at the moment that the MOSFET is turned on, the switching losses are significantly reduced.

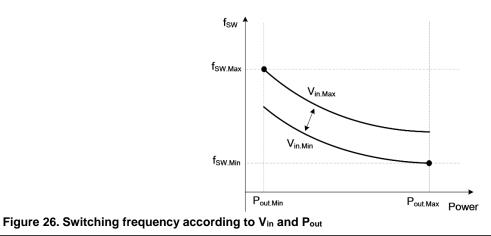

In the QR mode operation, the switching frequency fsw is changed according to the input voltage Vin and the output power Pout. Figure 26 shows the graph of the switching frequency according to the input voltage Vin and the output power Pout. As the Pout increases, the fsw decreases because longer charging time (on-time) is required to store more energy at the inductor. On the other hand, as the Vin increases, the fsw decreases because the same amount of energy can be stored within shorter charging time due to higher Vin.

LED

Cas and L

VGS

VDS

IL.

VGS

VDS

MAP3525B datasheet – **Quasi-Resonant Mode Buck Controller for LED Backlight**

# Design Guide

#### 1. Input Voltage and LED Voltage Setting

The input voltage is should be higher than the output voltage (the LED voltage) on the buck converter.

$$V_{in} > V_{LED} \tag{5}$$

The voltage of the LED bar is expressed as follows:

$$V_{LED} = V_F \times n \tag{6}$$

Where  $V_F$  is the voltage drop of a LED and *n* is the number of LEDs in the LED bar.

#### 2. Rcs Selection

In the condition where  $R_{REF}=R_{ADIM}$  and  $V_{ADIM}=3.3V$ , from (1), the current sensing resistor  $R_{CS}$  is calculated as follows:

$$R_{CS} = \frac{0.5V_{ADIM}}{I_{LED.max}} = \frac{0.5 \times (0.66 + 0.3 \times 3.3V)}{I_{LED.max}}$$

(7)

From (7), the minimum LED current is obtained as follows:

$$I_{LED.min} = \frac{0.5 \times (0.66 + 0.3 \times 0V)}{R_{CS}}$$

(8)

Where V<sub>ADIM</sub>=0V.

#### 3. Inductance Calculation

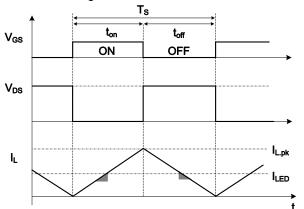

If the ideal CRM Buck converter as shown in Fig. 27, the ideal on-time is calculated as follows:

$$t_{on\_ideal} = \frac{V_{LED}}{V_{in} f_{sw}}$$

(9)

In the Ideal CRM Buck converter, the peak inductor current  $I_{L.pk}$  is twice the LED current  $I_{LED}$ . From (9), the ideal inductance of L is calculated as follows:

$$L_{ideal} = \frac{V_{in} - V_{LED}}{I_{L.pk}} t_{on\_ideal}$$

(10)

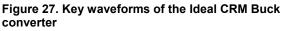

#### 4. Quasi-Resonant Time

In the QR Buck converter, the turn-on delay time  $t_{delay}$  is existed by the resonance between  $C_{ds}$  and L. Unfortunately, it is impossible to calculate the actual quasi-resonant time. The most of the parasitic capacitances affecting the resonance are unknown except the output capacitance  $C_{oss}$  of the MOSFET.

In order to operate close to CRM operation mode, the  $t_{delay}$  must be very small enough with minimal design impact. In the design example,  $C_{ds}$  was considered as 100pF.

From (4), the turn-on delay time  $t_{delay}$  is calculated as follows:

$$t_{delay} \approx \pi \sqrt{L \cdot C_{ds}}/2 \tag{11}$$

However, the calculated  $t_{delay}$  is not correct because the C<sub>ds</sub> is not real value and the  $t_{delay}$  can be changed by the ZCD detection timing (the turn-on timing).

We recommend using the measured  $t_{delay}$  for the converter design.

Figure 28. Key waveforms of the QR Buck converter

#### 5. Inductor Current

By the turn-on delay time  $t_{delay}$ , the inductor current decreases to negative. Therefore, the inductor peak current  $I_{L.pk}$  is slightly higher than the twice of the LED current  $I_{LED}$ .

The negative inductor current  $I_{L\_N}$  is estimated as follows:

$$I_{L_N} \approx -\frac{V_{LED}}{L} t_{delay} \tag{12}$$

However, the calculated  $I_{L_N}$  is not correct because the  $I_{L_N}$  decreases nonlinearly by the resonant.

We recommend using the measured  $I_{L\_N}$  for the converter design.

From (12), the peak inductor current  $I_{L,pk}$  is estimated as follows:

$$I_{L.pk} \approx 2I_{LED.max} - I_{L_N} \tag{13}$$

# 6. Switching Frequency

In the QR Buck converter, by the turn-on delay time  $t_{\text{QR}},$  the switching frequency  $f_{\text{SW}}$  is less than the target switching.

$$f_{SW} < f_{SW\_target} \tag{14}$$

During a single-switching period, the switching period  $T_s$  is expressed as follows:

$$T_s = t_{ON} + t_{OFF} = t_{ON} + t_{OFF}' + t_{delay}$$

(15)

The on-time  $T_{on}$  is obtained as follows:

$$t_{ON} = (I_{L.pk} - I_{L_N}) \frac{L}{V_{in} - V_{LED}}$$

(16)

The discharging time  $t_{OFF}$ ' is obtained as follows:

$$t_{OFF}' = I_{L.pk} \frac{L}{V_{LED}}$$

(17)

From (11), (15), (16) and (17) the switching frequency is obtained as follows:

$$f_{SW} = \frac{1}{t_{ON} + t_{OFF}' + t_{delay}}$$

(18)

K Magnachip is a registered trademark of Magnachip Semiconductor Ltd.